MOS 管入门:NMOS 与 PMOS 原理、对比与选型详解

- 电子技术

- 10小时前

- 33热度

- 0评论

1. MOS 管基础

NMOS 与 PMOS 是两种最常见的 MOSFET(场效应管)。理解 NMOS PMOS 区别的起点,是记住 MOS 管用电压控制电流,三极管用电流控制电流。

1.1 管脚说明

MOS 管有三个管脚,PMOS 和 NMOS 管脚名称完全相同:

| 管脚 | 英文 | 中文 | 作用 |

|---|---|---|---|

| G | Gate | 栅极 | 控制极,控制 S 与 D 之间的通断 |

| S | Source | 源极 | 载流子来源 |

| D | Drain | 漏极 | 载流子流出 |

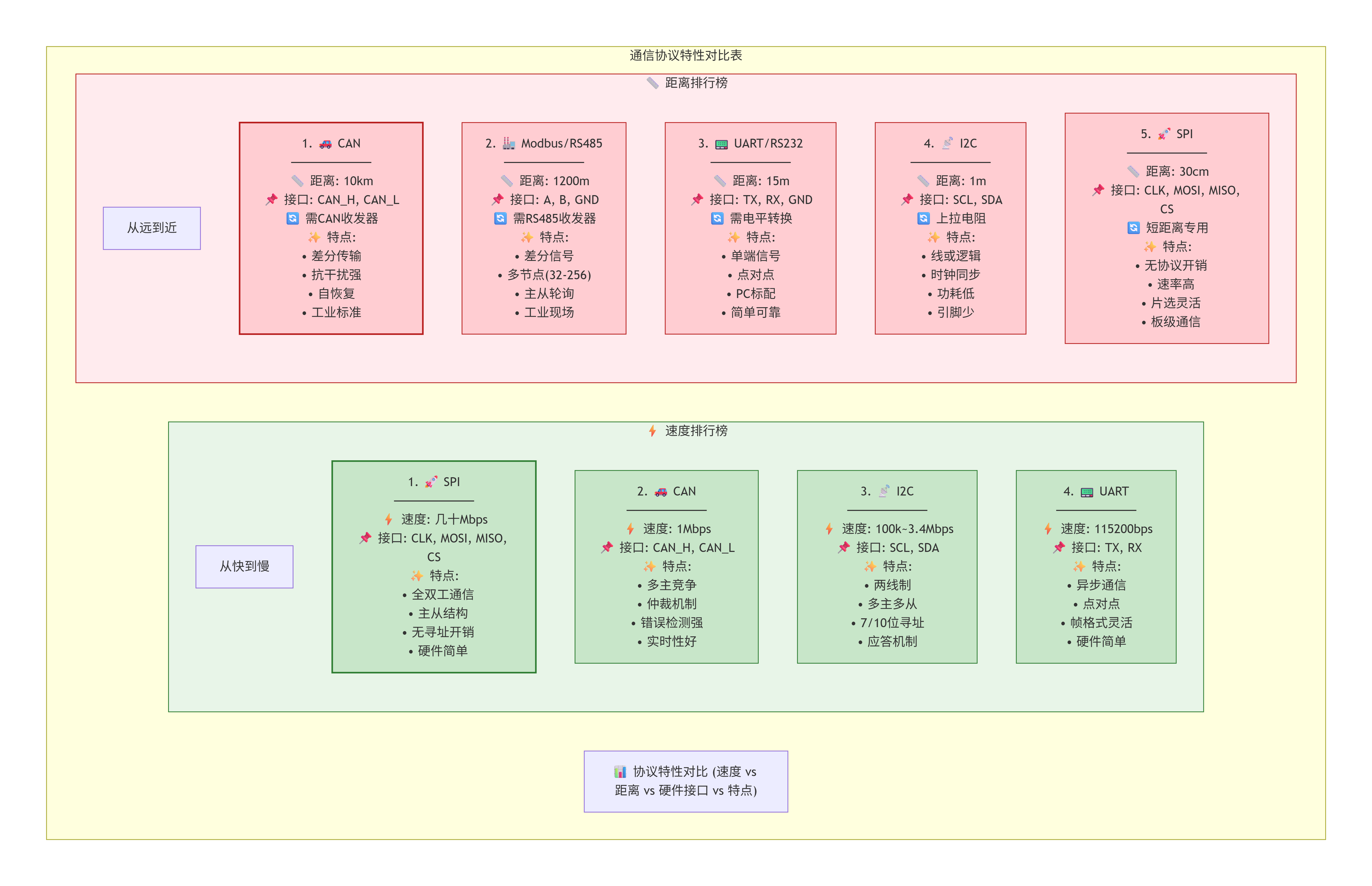

ℹ️ 源极识别方法:找到与箭头相连的管脚(不管箭头方向),该极即为源极 S。

- NMOS:电子从 S 流出,S 是 N 型半导体

- PMOS:空穴从 S 流出,S 是 P 型半导体

💡 符号快速辨认

- 箭头朝外(背离沟道)→ PMOS(口诀:朝外「放屁」,P = PMOS)

- 箭头朝内(指向沟道)→ NMOS

- PMOS 栅极有小圆圈;NMOS 栅极无小圆圈

- 箭头朝外(背离沟道)→ PMOS(口诀:朝外「放屁」,P = PMOS)

- 箭头朝内(指向沟道)→ NMOS

- PMOS 栅极有小圆圈;NMOS 栅极无小圆圈

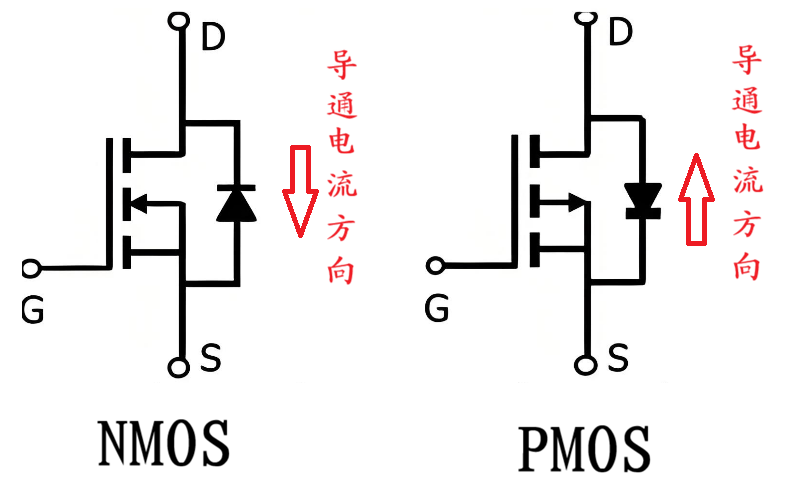

1.2 等效模型

- NMOS:Vgs 升高 → 沟道开启 → D 到 S 导通

- PMOS:Vgs 降低 → 沟道开启 → S 到 D 导通

2. 全称解析

物理结构上:NMOS 在 P 型衬底上做 N+ 区,用电子导电;PMOS 在 N 阱里做 P+ 区,用空穴导电。

NMOS

全称:N-channel Metal-Oxide-Semiconductor Field-Effect Transistor

中文:N沟道 金属-氧化物-半导体 场效应晶体管

| 字段 | 含义 |

|---|---|

| N-channel | N沟道(电子作为主要载流子) |

| Metal | 金属栅极(早期是金属,现多为多晶硅,名称保留) |

| Oxide | 氧化物绝缘层(SiO₂) |

| Semiconductor | 半导体(硅) |

| Field-Effect Transistor | 场效应晶体管(通过电场控制电流) |

ℹ️ NMOS 特点:高电平导通,主要用于将输出拉低到 GND,起下拉(Pull-Down)作用。

PMOS

全称:P-channel Metal-Oxide-Semiconductor Field-Effect Transistor

中文:P沟道 金属-氧化物-半导体 场效应晶体管

| 字段 | 含义 |

|---|---|

| P-channel | P沟道(空穴作为主要载流子) |

| Metal | 金属栅极 |

| Oxide | 氧化物绝缘层 |

| Semiconductor | 半导体 |

| Field-Effect Transistor | 场效应晶体管 |

ℹ️ PMOS 特点:低电平导通,主要用于将输出拉高到电源电压,起上拉(Pull-Up)作用。

NMOS vs PMOS 对比

| 项目 | NMOS | PMOS |

|---|---|---|

| 全称 | N-channel MOSFET | P-channel MOSFET |

| 沟道类型 | N 型沟道 | P 型沟道 |

| 载流子 | 电子(速度快) | 空穴(速度较慢) |

| 导通条件 | 栅极高电平(Vgs > Vth) | 栅极低电平(Vgs < Vth) |

| 电流方向 | D → S | S → D |

| 主要作用 | 下拉(Pull-Down) | 上拉(Pull-Up) |

| 输出拉至 | GND(低电平) | VDD(高电平) |

| 电路位置 | 放在下面(靠近地) | 放在上面(靠近电源) |

| 符号特点 | 箭头向内 | 箭头向外 |

| 栅极符号 | 无小圆圈 | 有小圆圈(低电平有效) |

| 导通电阻 Rdson | 较小 ✓ | 较大 |

| 价格 | 较低 ✓ | 较高 |

| 品种 | 较多 ✓ | 较少 |

💡 记忆口诀

P → Pull Up(P 负责拉高)

N → Pull Down(N 负责拉低)

P → Pull Up(P 负责拉高)

N → Pull Down(N 负责拉低)

NMOS 与 PMOS 导通条件判断

无论 PMOS 还是 NMOS,只需比较 G 极电压与 S 极电压的大小关系即可判断是否导通。

| 类型 | 导通条件 | 电流方向 | 说明 |

|---|---|---|---|

| NMOS | Ugs > 0(G 电压 > S 电压) | D → S | G 必须高于 S |

| PMOS | Ugs < 0(G 电压 < S 电压) | S → D | G 必须低于 S |

⚠️ 注意:节点电平从上到下依次减小,NMOS 的 G 必须高于 S,PMOS 的 G 必须低于 S,判断时务必先确认 S 极位置。

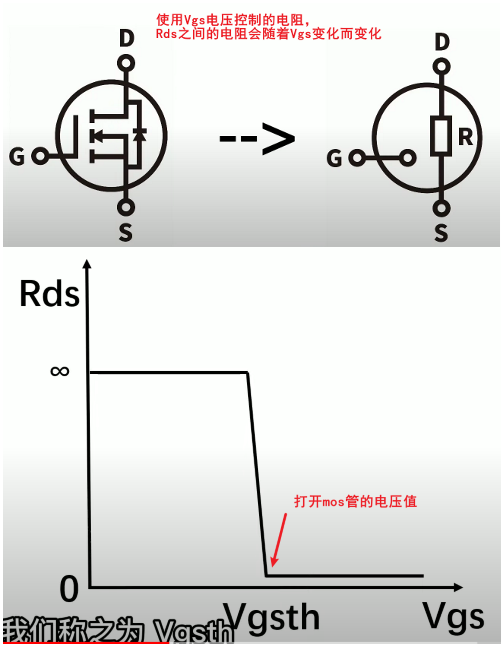

NMOS 与 PMOS 联合应用

GPIO 推挽(Push-Pull)输出级

STM32 GPIO 输出采用 PMOS + NMOS 组成推挽结构,能同时提供强拉高和强拉低能力。

ℹ️ 推挽原理

- 控制信号高:NMOS 导通(下拉),PMOS 截止 → 输出低电平

- 控制信号低:PMOS 导通(上拉),NMOS 截止 → 输出高电平

- 控制信号高:NMOS 导通(下拉),PMOS 截止 → 输出低电平

- 控制信号低:PMOS 导通(上拉),NMOS 截止 → 输出高电平

MOS 管选型参数

MOS 管选型时,NMOS PMOS 区别在性能参数上同样显著,需重点关注以下四个参数:

| 参数 | 全称 | 说明 |

|---|---|---|

| 封装 | Package | 封装越大,承受功率越大 |

| Vgsth | Gate-Source Threshold Voltage | 打开 MOS 所需最小 Vgs,应小于驱动高电平值 |

| Rdson | On-State Drain-Source Resistance | MOS 导通时 D-S 间电阻,越小越好(分压发热小) |

| Cgs | Gate-Source Capacitance | G 与 S 之间的寄生电容,影响开关速度 |

⚠️ 选型权衡:Rdson 与 Cgs 成反比——Rdson 越小,Cgs 越大,开关速度越慢。需根据应用场景平衡选择。

参考资料

延伸阅读:NMOS and PMOS: What's the Difference,MOSFET - Wikipedia